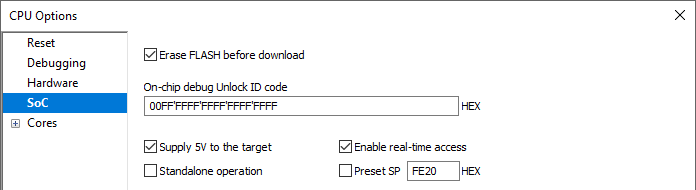

SoC

Open Hardware | CPU Options | SoC.

Erase FLASH before download

Check the option if complete flash should be erased prior to the debug download. Otherwise, only the necessary sectors are erased.

On-chip debug Unlock ID code

After reset, the 10 bytes ID code specified in winIDEA is compared with 10 bytes from memory location (0x00C4 – 0x00CD). If 16-bytes ID code is specified, it is compared with 16 bytes from memory location (0x00C6-0x00D5). If invalid ID code is specified, emulation will not start. The CPU considers:

•10 x 0xFF invalid code in the case of 10-bytes code, or

•16 x 0xFF invalid code in the case of 16-bytes code.

Supply 5V to the target

When enabled in winIDEA, the emulator supplies 5V at the pin 4 (VCC) on the debug connector.

Enable real-time access

When checked, RT access is enabled (an additional monitor is used and loaded to flash).

Standalone operation

When this option is enabled, only the user’s code without OCD monitor is loaded to internal flash during download. The emulator is working as a flash programmer.

After the debug download is finished, the NO CONNECTION debug status is displayed.

Preset SP

The Stack Pointer (SP) register must be initialized for the OCD monitor to function. Since generating the signal reset results in undefined SP contents, the debugger initializes the SP register to 0xFE20. You can preset the SP to any value by using the Preset SP option.