MMU Support

Normally MMU is initialized by Boot Assistant Module (BAM). After reset the CPU first executes code from BAM, which initializes MMU, then reads reset configuration word and starts running user code.

However, the debugger must initialize MMU when some debug option is used that circumvent BAM to be initialized upon reset (e.g. overriding startup PC using ‘CPU Setup/Advanced’ dialog). The debugger can configure MMU through Initialization sequence use. When no such option is used, the debugger doesn’t need to configure MMU.

Below is an excerpt from the initialization file (.ini), which initializes MPC5554 MMU in case when the program counter is preset (overridden) after the CPU reset.

S "SPR":(270) L 0x10000000

S "SPR":(271) L 0xC0000500

S "SPR":(272) L 0xFFF0000A

S "SPR":(273) L 0xFFF0003F

I 7C0007A4

S "SPR":(270) L 0x10030000

S "SPR":(271) L 0xC0000400

S "SPR":(272) L 0x40000008

S "SPR":(273) L 0x4000003F

I 7C0007A4

S "SPR":(270) L 0x10040000

S "SPR":(271) L 0xC0000500

S "SPR":(272) L 0xC3F00008

S "SPR":(273) L 0xC3F0003F

I 7C0007A4

S "SPR":(270) L 0x10010000

S "SPR":(271) L 0xC0000700

S "SPR":(272) L 0x00000000

S "SPR":(273) L 0x0000003F

I 7C0007A4

S "SPR":(270) L 0x10020000

S "SPR":(271) L 0xC0000700

S "SPR":(272) L 0x20000000

S "SPR":(273) L 0x2000003F

I 7C0007A4

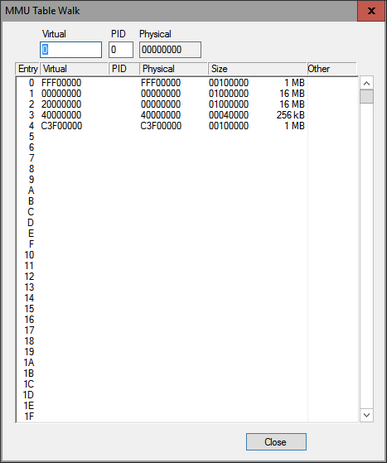

MMU Table Walk window

Virtual to physical address mapping of the individual memory pages is displayed in the MMU Table Walk window. The window can be selected from the Debug / MMU Table Walk menu for all CPUs with MMU. A direct entry of a virtual address is possible.

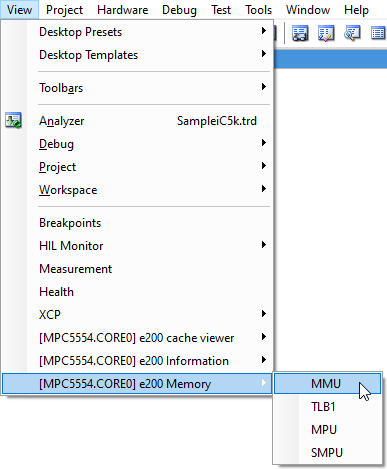

Exhaustive information on MMU and also certain core related information are displayed through the plugin windows.

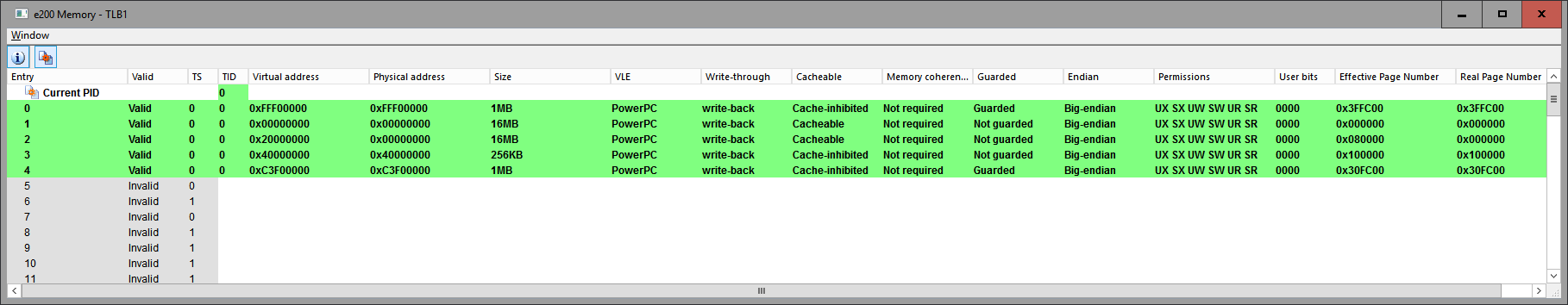

Memory window

For the detailed information on TLBs (Translation Lookaside Buffer), open the Memory window from the Plugins menu. It displays parameters like virtual address, physical address, block size, VLE, Write-through, Guarded, Cacheable, Memory Coherence, etc.