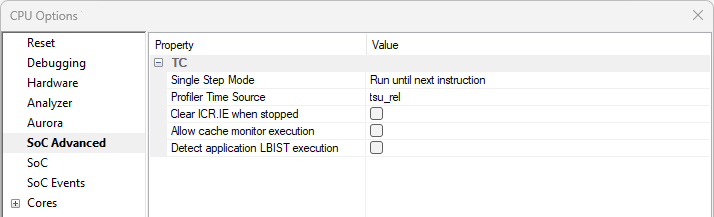

SoC Advanced

Open Hardware | CPU Options | SoC Advanced.

Single Step Mode

•Run until next instruction - The core will run until the next instruction. If an interrupt or a trap is pending, it will be serviced.

•Stop after op-code executed - The core will execute precisely one instruction. If an interrupt or a trap is pending, a single step will result in a jump to the corresponding handler.

Profiler Time Source

This option specifies which timestamp mechanism is used for trace configuration when trace is configured automatically by winIDEA. More information is given in the in-line help.

Clear ICR.IE when stopped

Enable this option to disable TriCore interrupts during single stepping.

|

AURIX TC3xxx step B devices: A peripheral module STM (System Timer Module) is normally suspended and used to generate periodic interrupts, however in this case STM logic is not suspended. |

Allow cache monitor execution

The TriCore architecture does not permit direct access to some of the cached regions (e.g. LMU) through the debug interface. When enabling this option, a monitor is loaded in RAM and executed by the SoC which reads the cached regions and writes them into memory mapped space. Cache is actually only accessed by code executing on the CPU.

This causes that some variables cannot be read and thus not be displayed correctly in the Watch window(s). Enable this option to read affected memory regions using a monitor. The monitor can only be ran when the SoC is halted, therefore real-time access of the cached memory is not possible.

|

Allow cache monitor execution may affect application execution. |

Detect application LBIST execution

Reconnect to the SoC when LBIST is executed by user code and the debug is protected with debug password in the UCBs.

Stop after application reset

Stop the execution of user application.