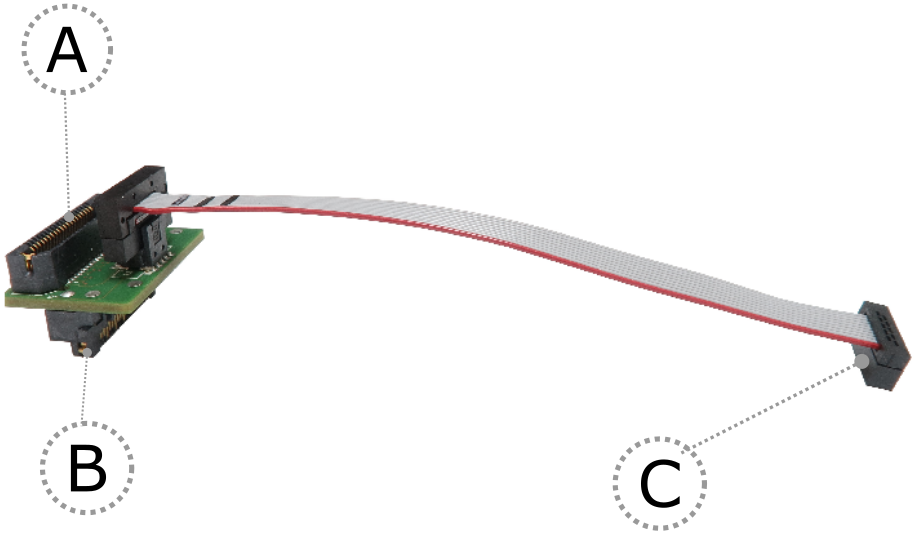

40-pin Samtec ERF8 to 10-pin CoreSight + 40-pin Samtec ERF8 HSSTP Converter

Normally 40-pin ERF8 ARM HSSTP connector provides both, ARM HSSTP trace interface and JTAG or SWD debug interface. However, some targets for some reason don’t connect debug interface to this connector and provide the debug JTAG/SWD interface on a separate debug connector (10-pin 1.27mm CoreSight). Using this adapter, the Active Probe can be properly connected to such target.

|

This converter is required only when the Active Probe is to be connected to the embedded target where the 40-pin Samtec ERF8 target debug connector doesn’t have the debug JTAG/SWD interface physically connected but has it connected instead to the available 10-pin 1.27 mm CoreSight target debug connector. The adapter doesn’t come along the Active Probe and has to be ordered separately. |

The converter has the following pinouts:

A – 40-pin Samtec ERF8 connector providing merged JTAG/SWD debug signals (C on the image) and the HSSTP trace signals (B on the image) signals, to which the Active Probe connects then.

B – 40-pin Samtec ERF8 connector which connects to target development board with 40-pin Samtec ERF8 connector exposing only the HSSTP trace signals.

Signal Direction |

Signal Description |

Signal |

Pin |

Pin |

Signal |

Signal Description |

Signal Direction |

|---|---|---|---|---|---|---|---|

O |

HSSTP Lane 4 |

Tx4_P |

1 |

2 |

Vref |

Reference Voltage |

I |

O |

HSSTP Lane 4 |

Tx4_N |

3 |

4 |

|

JTAG |

O |

|

Ground |

GND |

5 |

6 |

GND |

Ground |

|

O |

HSSTP Lane 2 |

Tx2_P |

7 |

8 |

NC |

Not Connected |

|

O |

HSSTP Lane 2 |

Tx2_N |

9 |

10 |

NC |

Not Connected |

|

|

Ground |

GND |

11 |

12 |

GND |

Ground |

|

O |

HSSTP Lane 2 |

Tx0_P |

13 |

14 |

|

JTAG |

O |

O |

HSSTP Lane 2 |

Tx0_N |

15 |

16 |

|

JTAG |

O |

|

Ground |

GND |

17 |

18 |

GND |

Ground |

|

O |

HSSTP Clock |

CLK_P |

19 |

20 |

|

Reset |

O |

O |

HSSTP Clock |

CLK_N |

21 |

22 |

NC |

Not Connected |

|

|

Ground |

GND |

23 |

24 |

GND |

Ground |

|

O |

HSSTP Lane 1 |

Tx1_P |

25 |

26 |

NC |

Not Connected |

|

O |

HSSTP Lane 1 |

Tx1_N |

27 |

28 |

NC |

Not Connected |

|

|

Ground |

GND |

29 |

30 |

GND |

Ground |

|

O |

HSSTP Lane 3 |

Tx3_P |

31 |

32 |

NC |

Not Connected |

|

O |

HSSTP Lane 3 |

Tx3_N |

33 |

34 |

NC |

Not Connected |

|

|

Ground |

GND |

35 |

36 |

Reserved |

|

|

O |

HSSTP Lane 5 |

Tx5_P |

37 |

38 |

Reserved |

|

|

O |

HSSTP Lane 5 |

Tx5_N |

39 |

40 |

Reserved |

|

|

40-pin Samtec ERF8 pinout

Blue colored signals are trace signals.

C – 10-pin CoreSight connector which connects to the target development board exposing JTAG/SWD debug interface.

Signal Direction |

Signal Description |

Signal |

Pin |

Pin |

Signal |

Signal Description |

Signal Direction |

|---|---|---|---|---|---|---|---|

I |

Reference Voltage |

Vref |

1 |

2 |

SWDIO/TMS |

SWD/JTAG |

I/O |

|

Ground |

GND |

3 |

4 |

SWCLK/TCK |

SWD/JTAG |

O |

|

Ground |

GND |

5 |

6 |

SWO/TDO |

SWD/JTAG |

I |

|

Not Connected |

KEY |

7 |

8 |

NC/TDI |

Not Connected / JTAG |

O |

|

Ground |

GND |

9 |

10 |

nRESET |

Reset |

I/O |

10-pin CoreSight pinout

Signal Direction is described from the BlueBox perspective.