Trace Multiplexer (MUX)

The MUX allows connecting the POBs to the various TriCore CPUs implemented on the chip. The TC3xx AURIX generation implements three POBs. However, some TC3xx derivatives include up to six cores. Thus, in these cases only three out of all available cores can be connected to a POB.

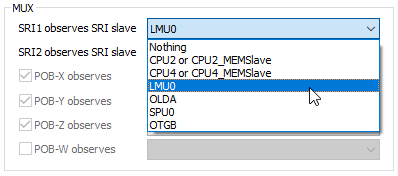

There are additional multiplexers attached to the Bus Observation Block (BOB) connected to the System Resource Interconnect (SRI). These multiplexers allow select specific SRI slaves to be connected to the SRI BOB, e.g. LMU RAM or specific CPU MEMSlaves.

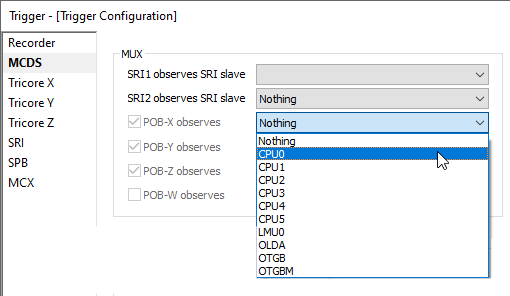

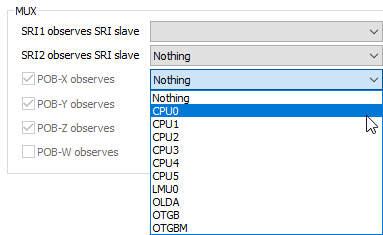

The Trace Multiplexers are represented by the MUX configuration section in the Analyzer Configuration | Manual Trigger/Recorder configuration | Trigger Configuration dialog | MCDS.

The Processor Observation Block X (POB X) can, for instance, be connected to either nothing, to any CPU, LMU, OLDA, OTGB or OTGBM.

|

With the AURIX TC2xx family only the two POBs X and Y are available, whereas the AURIX family TC3xx implements three POBs X, Y and Z. |

The Bus Observation Block connected to the SRI (BOB SRI 1/2) can be hooked up to various SRI slaves, for instance the processor local RAMs or LMU RAM.