Arm Cortex-M MPU

In this topic:

Introduction

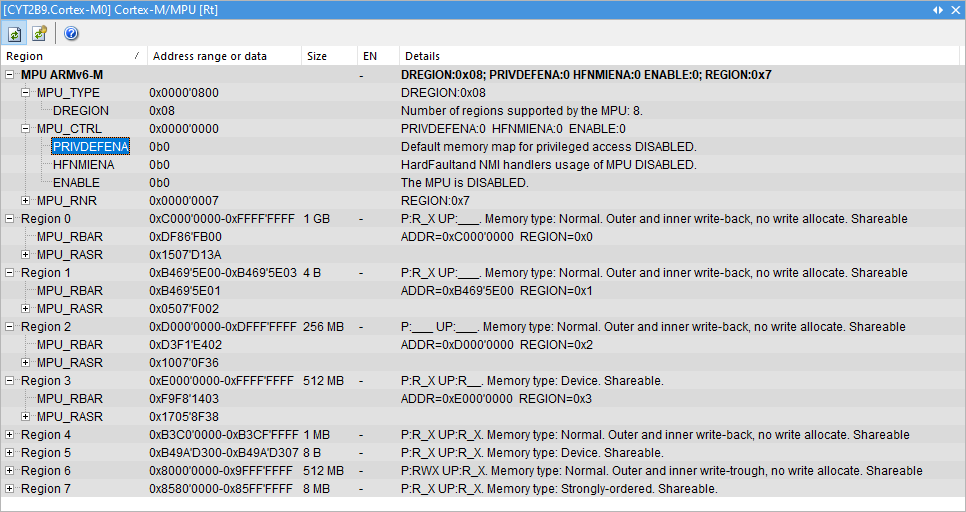

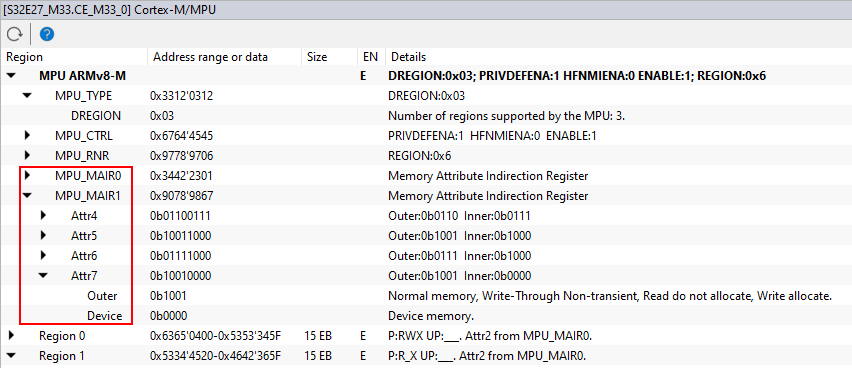

The Cortex-M MPU is a core plugin and it is used to view the number of Cortex-M MPU regions, with the location address, size, access permissions, and memory attributes of each region.

Supported architectures

Cortex-M MPU supports following architectures:

•ARMv6-M

•ARMv7-M

•ARMv8-M

|

For a correct configuration of the MPU refer to the Arm manual. |

The plugin can be loaded by selecting View | [<device>.COREn] Cortex-M | MPU. Information is displayed when a debug connection is established.

Toolbar

Button |

Description |

|---|---|

|

Manually update the window |

|

Go to winIDEA Help |

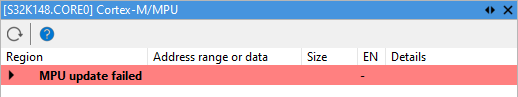

Status row

Red background color - Last read status. Note that MPU update failed warning is displayed if the connection to the CPU MPU is not established.

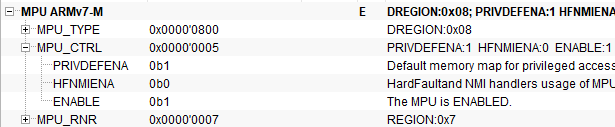

EN - Enabled MPU (“E” for enabled range, “-” otherwise)

•Details - Quick information about general MPU parameters

•Status bar can also be extended to show detailed view of the registers MPU_TYPE, MPU_CTRL and MPU_RNR

List of MPU Regions

•Address range or data - Address range (inclusive). In a case of a region with size 0 B, address range is written only with start address

•Size - Specified size of the region

•EN - “E” for enabled range, “-” otherwise

•Details - Privileged (P) and unprivileged (UP) access right, followed by attributes description

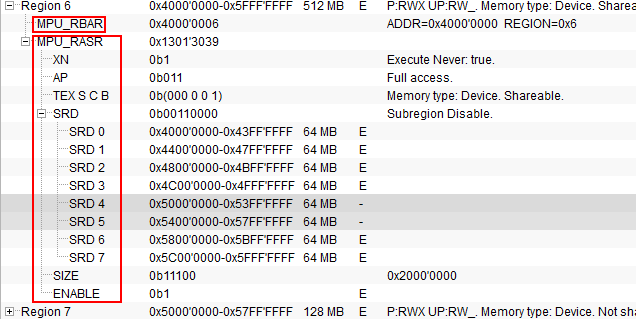

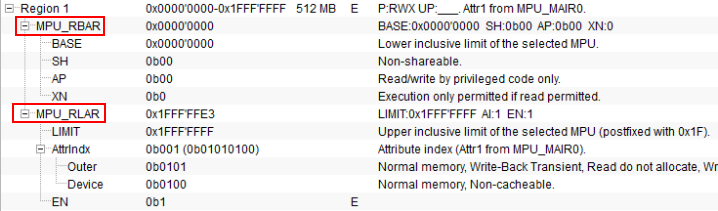

Expanded Region

The expanded region contains a detailed view of register values for the selected region.

ARMv6-M and ARMv7-M

MPU_RBAR and MPU_RASR registers

Region details for CPUs ARMv6-M and ARMv7-M contain values of MPU_RBAR and MPU_RASR registers for a selected region.

MPU_RASR register

Value from register MPU_RASR is further sliced into separate fields:

•XN - Execute never

•AP - Access permission

•TEX S C B - Memory type attributes

•SRD - Subregion disable field

•Size

•ENABLE

ARMv8-M

View for ARMv8-M CPUs contains additional data about two MPU_MAIR registers inside the expanded status row. In case when the CPU implements Security Extensions (also referred as Arm TrustZone for Armv8-M), the view contains data from the current security state of the CPU.

Attribute field - Attr

Each of both MPU_MAIR registers contains 4 Attribute fields, which are expandable to display detailed explanation of the attribute’s value.

MPU_RBAR and MPU_RLAR registers

Details for MPU regions on CPU ARMv8-M contain values of corresponding registers MPU_RBAR and MPU_RLAR. Each of them is further expandable to explain register values in more detail.

Context menu

Right-click in the plugin window to open the context menu.

Copy Python access snippet - Copy SDK code snippet to extract the content from the plugin window.

Auto Fit - Arrange all the columns to fit in the plugin window.

Options - Set colors and fonts.

Help - Open winIDEA Help.

|

To display or hide columns, right-click on a column header and select what you want to see. |