Manual Multi-Core Synchronization

In this topic:

•

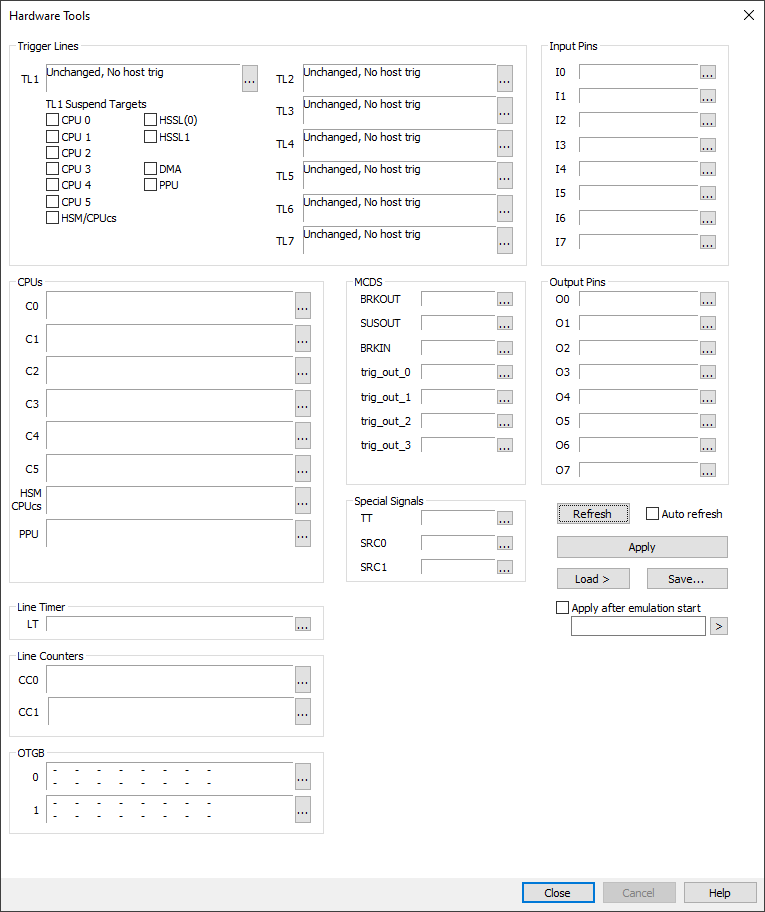

Manual synchronization can be achieved via a winIDEA configuration dialog of the on-chip OCDS module. For more information, refer to the OCDS chapter of the TriCore user manual. Open Hardware | SoC Debug Module.

Trigger Lines TL1-TL7

TriCore devices have internal 7 trigger lines to where Break, Suspend or Trigger Events from Cores, MCDS (trace) or Trigger Pins can be connected.

TL1 Suspend Targets

Simplified view of the Trigger line 1, which is used to suspend Targets.

CPUs

Each core has SUSIN, BRKIN, BRKOUT and HALT signals. For each core you can specify to which trigger line these signals are connected.

HSM / MCDS

Specify to which trigger line these signals are connected.

More resources

•Multi-Core Debugging - Troubleshooting tips

•

•How to Suspend Peripheral devices