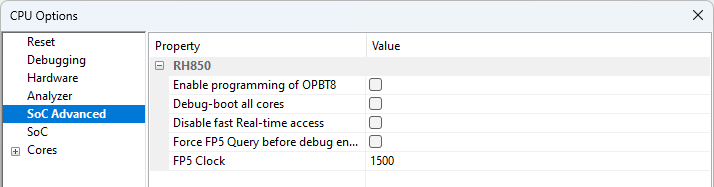

SoC Advanced

Open Hardware | CPU Options | SoC Advanced page.

RH850G3

RH850G4

Enable programming of OPBT8 (only RH850G3 devices)

If checked winIDEA attempts to protect high-end RH850/F1H, F1KM/F1KH and P1x-C devices from getting permanently locked. This protection can be optionally turned off in the dialog window.

Debug-boot all cores (only RH850G3 devices)

Control booting the cores in the F1KM/F1KH devices. Set the option to debug all cores after RESET, even if ICUM is enabled. If not checked when ICUM is enabled, PE cores wait to be enabled by the ICUM.

Enable this option if more than one core is active.

Disable fast Real-time access

If the option Disable fast Real-time access is checked, the memory is accessed through MAU instead of Sampling RAM.

Force FP5 Query before debug entry

|

Supported in RH850G3 based SoCs. Not applicable to RH850G4, the RH850/E2x/U2x SoCs. |

In some cases a scripted FP5 Query could fail if debug-mode entry is performed. Right before the debug entry the user code will run for a couple of 10s of milliseconds, configure the PLL and a subsequent FP5 connection may fail.

The option should also be used for reconfiguring devices that are fresh from the factory as they are usually preset for JTAG debug connection, which is not supported. FP5 Query will set the device to LPD4 debug port. Note, this option will be reset the next time the workspace is opened.

Solution:

1. Turn on the BlueBox.

2. Power-cycle the CPU.

3. Enable Force FP5 Query before debug entry.

4. Perform CPU Reset command.

More information available in the in-line help as well.

|

Note that Debug-boot all cores and Auto Start options are mutually exclusive and should not be used at the same time. |

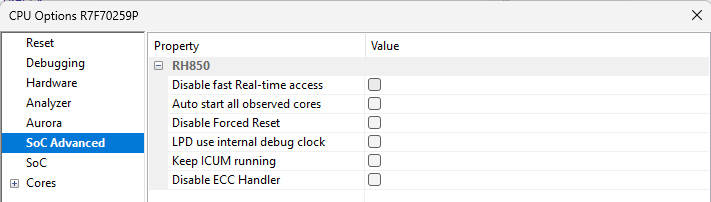

RH850G4 Specific Options

Auto start all observed cores

Checked Auto start all observed cores option enables automatic start of all observed cores at debug entry (via BOOTCTRL register). If this option is not set, secondary cores are not started automatically, so the customer's application needs to enable them.

[CPU1] Initial STOP status is shown until the secondary cores are started.

Disable Forced Reset

Normally this should be off. The option might help when OS doesn't start properly. A side-effect is that cores don't stop consistently at their respective reset vectors.

LPD use internal debug clock

This LPD4 debug interface option is intended for boards without LPDCLKOUT return debug clock connected. Debug performance may be limited. Please reduce LPD clock frequency in case of instabilities. Supported for iC5700 and iC7 BlueBox.

Keep ICUM Running

If enabled, ICUM is kept running after the SoC reset, to be able to start up other cores. This option is only effective if ICUM is enabled and set as the boot core; it has no effect during programming. In combination with the option Hardware | CPU Options | Reset | Configured boot core, various startup and FLASH programming scenarios can be implemented.

Disable ECC Handler

Set this debug option to turn off winIDEA handling ECC registers on memory access when assessing debugger influence on the application execution. Normally this should be off.