Memory Spaces

A Memory Space is assigned to a core or an SMP group. Within it, virtual (core) memory accesses are separated from other memory spaces by hardware logic. In each, one application is executing. If a core supports multiple protection levels, specify memory spaces for every protection level in which an application will be executing.

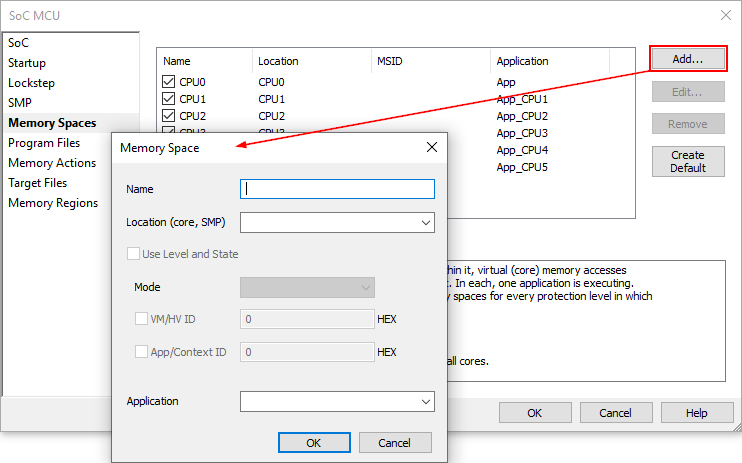

To configure Memory Spaces select Debug | Configure Session | SoC | Memory Spaces page.

Create Default (recommended) - Add Memory Spaces for all cores.

Add - Add a Memory Spaces.

If you're not interested in certain cores, or don't have the Symbol file available, disable the respective Memory Space by unchecking it.

Memory Space dialog

Name - Give it a meaningful name.

Location (core, SMP) - Define the location.

Use Level and State - Enable if multiple processes will execute on this core. The following fields specify how the MMU is configured for this memory space.

Mode - Specifies the core state (Exception Level, secure/non-secure):

•VM/HV ID - Specifies the Virtual machine ID - typically written by hypervisor into the VMID register.

•APP/Context ID - Specifies the Process ID - typically written by an RTOS into CONTEXTID/PID register.

Application - Select the application that belongs to the Memory Space.

|

Invalid cores which are Lockstep bound are marked red. |

Memory Spaces for specific microcontroller architecture

These microcontroller architectures support multiple memory spaces. On other architectures (not listed below) the memory space can be omitted.

Arm Cortex

Memory Area |

Description |

View type |

|---|---|---|

Virtual |

Current / default mode |

Core View |

IP |

Intermediate Physical |

|

SP |

Secure Physical |

|

NP |

Normal Physical |

|

PLnS |

Privilege Level n Secure |

|

PLnN |

Privilege Level n Normal |

|

ELnS |

Exception Level n Secure |

|

ELnN |

Exception Level n Normal |

|

APB_0 |

Advanced Peripheral Bus |

Bus View |

AXI_0 |

Advanced Extensible Interface |

|

AHB_n |

Advanced High-Performance Bus |

NXP/ST Power Architecture

Memory Area |

Description |

View type |

|---|---|---|

Virtual |

Current / default mode |

Core View |

PMR |

Performance Monitor Registers |

|

SPR |

Special Purpose Registers |

|

DCR |

Device Control Registers |

|

Physical |

|

Bus View |

Renesas RH850

Memory Area |

Description |

View type |

|---|---|---|

Virtual |

Current / default mode |

Core View |

Physical |

|

Bus View |

Infineon TriCore

Memory Area |

Description |

View type |

|---|---|---|

Virtual |

Current / default mode |

Core View |

Physical |

|

Bus View |