TriCore Counters

In this topic:

Introduction

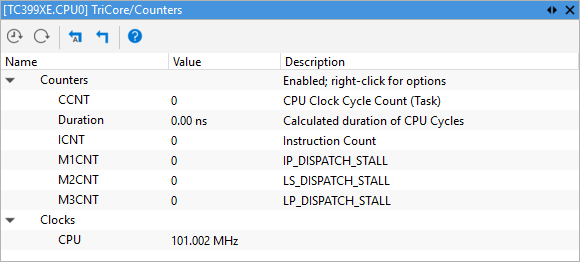

Counters is a separate core window of the TriCore plugin. It features an enhanced view of Core Debug Controller (CDC) counters and displays the CPU Clock. You can configure counters and breakpoints to measure CPU cycles and time.

To load the plugin select View | [<device.core>] TriCore | Counters. Information is displayed when a debug connection is established.

Button |

Description |

|---|---|

|

Switch to real-time update |

|

Refresh the window (F8) |

|

Reset CDC counters automatically when the CPU starts running |

|

Reset CDC counters |

|

Go to winIDEA Help |

Counters

Section displays counter values and descriptions for CCNT, Duration, ICNT, M1CNT, M2CNT and M3CNT.

Counters with Sticky Overflow bit set to 1 are displayed with the SOvf prefix.

Clocks

Display the current CPU frequency.

Context menus

The Counters core window consists of two context menus:

•General options

•Counters option

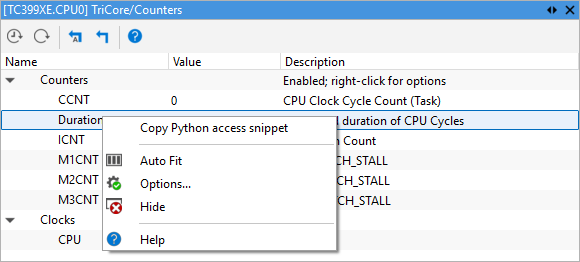

General context menu

Right-click anywhere in the content part of the window to open a context menu.

Copy Python access snippet - Copy SDK code snippet to extract the content from the plugin window.

Auto Fit - Arrange all the columns to fit in the plugin window.

Options - Set colors and fonts.

Help - Open winIDEA Help.

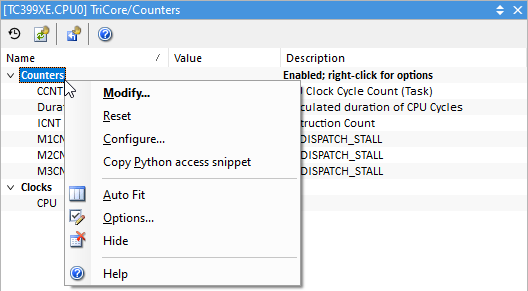

Counters context menu

Right-click on the Counters item to open a Counters context menu. It contains the following additional options:

Modify - Changes the current setting of the counters. See Modifying Counters chapter for more information.

Reset - Resets the values of the counters to zero.

Configure - Changes how the counters are configured after a CPU reset. See Configuring Counters chapter for more information.

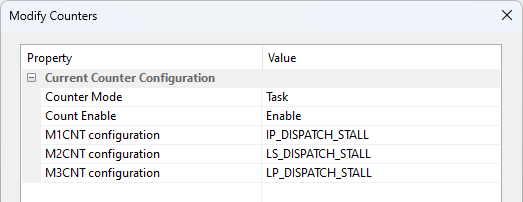

Modifying Counters

Current Counter configuration in the Modify Counters dialog shows current values of register CCTRL. It also enables changing current values of this register. Options take effect when the OK button is pressed. Since these values are stored in a register, they are lost after CPU reset.

Counter Mode - Choose Task if you want counters to increment only between hardware breakpoints, or Normal if you want them to increment continuously.

Count Enable - Enable or disable the counters.

MxCNT - Chooses which metric is counted by a specific counter.

Multi-count Registers

Detailed descriptions with mapping are available in the Infineon AURIX Microcontrollers User Manual and in the in-line help within winIDEA.

TC Core Architecture |

M1CNT |

M2CNT |

M3CNT |

|---|---|---|---|

TC1.6E |

IP_DISPATCH_STALL PCACHE_HIT TOTAL_BRANCH |

LS_DISPATCH_STALL PMEM_STALL PCACHE_MISS |

DMEM_STALL |

TC1.6P, 1.6.2P and TC1.8 |

IP_DISPATCH_STALL PCACHE_HIT DCACHE_HIT TOTAL_BRANCH |

LS_DISPATCH_STALL PCACHE_MISS DCACHE_MISS_CLEAN PMEM_STALL |

LP_DISPATCH_STALL MULTI_ISSUE DCACHE_MISS_DIRTY DMEM_STALL |

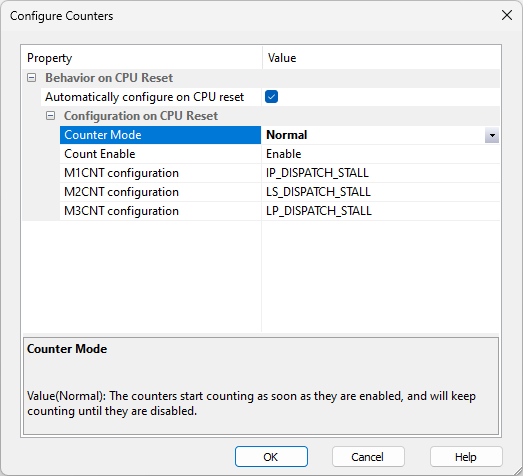

Configuring Counters

The Configure Counters dialog defines initial values for counter registers after CPU reset or start of debug. Values for section Configuration on CPU Reset are persisted in the workspace file (for current core) and therefore available after a winIDEA restart.

Automatically configure on CPU reset - Automatically apply configuration on reset. It is recommended to check this option only in primary winIDEA (for all cores) since secondary winIDEA does not support configuration of counters.

To observe CPU0 core run time, enable this option and set Counter Mode to Normal.

Configuration on CPU Reset - Configuration settings, which are applied on reset, when Automatically configure on CPU reset option is enabled.

|

Set the configuration to be persistent throughout the winIDEA workspace or for a current configuration. |