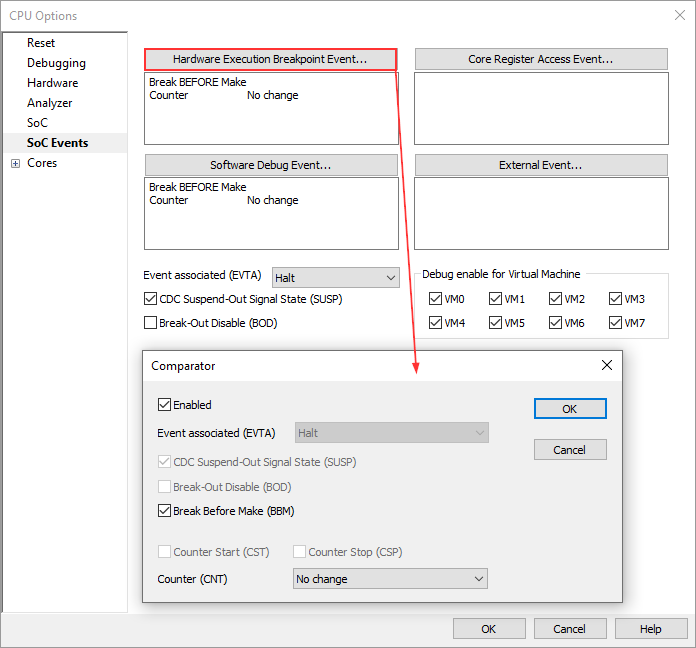

SoC Events

It is possible to configure individual event actions for hardware execution breakpoint event (TRxEVT), core register access event (CREVT), software debug event (SWEVT) and external break input event (EXEVT).

Refer to Access Breakpoints chapter for available event actions and explanation.

|

In the CPU Options | SoC Events dialog, the following options: •Event associated (EVTA) •CDC Suspend-Out Signal State (SUSP) •Break-Out Disable (BOD) only apply to TriCore V1.8. For TriCore V1.6 & V1.6x, use the same-named options from the Comparator dialog. |

|

In the CPU Options | SoC Events | Comparator dialog, the following options: •CDC Suspend-Out Signal State (SUSP) •Break-Out Disable (BOD) are not supported for TC4x, since it doesn't have action control per breakpoint. The action is global for all breakpoints and can be configured in CPU Options | SoC Events. It is not possible to measure running time between two breakpoints on TC4x as it was with TC3xx. |

Event Associated (EVTA)

Disabled - The event is disabled and no actions occur: the suspend-out signal and performance counter control ignore the event

None - No action is implemented through the EVTA field of the event’s register however the suspend-out signal and performance count still occur as normal for an event.

Halt - The Debug Action Halt, causes the Halt mode to be entered where no more instructions are fetched or executed. While halted, the CPU does not respond to any interrupts.

Breakpoint Trap - The Breakpoint Trap enters a Debug Monitor without using any user resource. Refer to TriCore Architecture manual for more details.

Breakpoint Interrupt - One of the possible Debug Actions to be taken on a Debug Event, is to raise a Breakpoint Interrupt. The interrupt priority is programmable and is defined in the control register associated with the breakpoint interrupt. Refer to TriCore Architecture manual for more details.

CDC Suspend-Out Signal State (SUSP) - The suspend-out signal is asserted when a debug event occurs. It is up to the user then to configure according peripheral module to act upon asserted suspend-out signal.

Break-Out Disable (BOD) - When this option is checked, BRKOUT signal is not asserted. This takes priority over any assertion generated by the EVTA field.

Debug enable for Virtual Machine - If virtual machines are available on the currently selected SoC, select which of them you wish to debug and/or trace. In virtual machines, where debug is disabled, breakpoints will not be hit and trace data will not be generated.