AMBA AHB Trace Macrocell (HTM)

In this topic:

Introduction

The CoreSight Advanced Microcontroller Bus Architecture (AMBA) Advanced High-performance Bus (AHB) Trace Macrocell (HTM) is a real-time trace module capable of address and data tracing of the AHB bus. The AHB bus is an internal interconnect bus connecting internal functional blocks in system-on-a-chip (SoC).

HTM captures the AHB activities of the AHB you want to monitor and the trace data is output using the AMBA Trace Bus (ATB) interface. The trace data is merged with trace data from other trace sources, such as the Embedded Trace Macrocell (ETM), to produce a single trace data stream. Depending on the implementation, the trace data can be sent directly to the trace port through the Trace Port Interface Unit (TPIU) or alternatively the data can be stored in the Embedded Trace Buffer (ETB).

The HTM can also interface with the Embedded Cross Trigger (ECT) so that events from other CoreSight devices, such as the ETM, can be used to drive the HTM or events from the HTM can be used to drive other CoreSight devices.

Each of different trace units also incorporates its own triggering system which can make for a quite complex trigger configuration on CPUs with multiple trace units on-board. All trace sources on Cortex based CPUs output trace information in a byte oriented stream protocol and this is the key factor that allows multiple trace sources to be output over a single trace port in a merged trace stream which is then recorded by BlueBox trace hardware.

HTM provides information for:

•AHB Bus read/write transactions (address & data value)

•Bus utilization

•Time correlation between the bus access (HTM), Program flow (ETM) and Data access (ETM & DWT)

HTM Configuration dialog

HTM Trigger Configuration is accomplished via Manual Trace Configuration. You can open this dialog via View | Analyzer | Analyzer Configuration | Manual Hardware Trigger | Configure | HTM.

Enabled - Enable the HTM configuration dialog.

Enable address packets - Make sure this option is enabled.

Enable AUX packets - Make sure this option is enabled.

Enable data packets - Make sure this option is enabled.

Enable cycle counter packets - Make sure this option is enabled.

Enable multiple triggers - Make sure this option is enabled.

AHB Slave Port - Select AXBS Bus masters. Number of options depends on the selected microcontroller.

AUX Information - Select suitable option from the drop-down menu.

FIFO level - Select FIFO level.

Trigger - Boolean combination for defining the Trigger.

Enabling Trace

Event - Boolean combination for defining Event.

Start / Stop - Check this option and include / exclude start and stop address. The four check boxes in the Start and Stop rows represent four comparators.

In the example below trace starts at address of comparator 0; and stops at the address of comparator 1.

Exclude Only check boxes - Include / exclude comparators from trace. The two Inc and Exc rows each of four check boxes under Exclude Only option represent four comparators.

In the example below comparator 1 is included in trace; comparator 1/2 is excluded from trace.

Range - Include / exclude ranges. The two Inc and Exc rows each of four check boxes under Range option represent four comparators.

In the example below comparator 1/2 and 3 define the trace range.

Address comparators

Select a single address or a range. The four rows represent four comparators:

•0/0 - Comparator 0

•1 - Comparator 1

•1/2 - Comparator 2

•3 - Comparator 3

Bus Data Trace

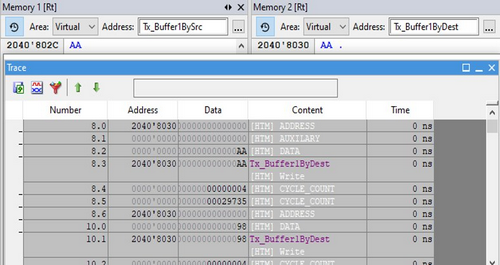

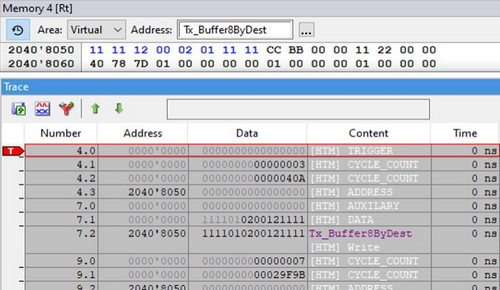

Example displays memory to memory transfer generated by the DMA Master in a single request.

HTM provides the address and data trace information about AXBS buses. HTM64 can be used to trace 64-bit and 32-bit wide data buses whereas HTM32 can be used to trace 32-bit wide data buses only. Example displays memory to memory transfer (8-bit and 64-bit) generated by the DMA Master in a single request on the S32K344 device.

8-bit data transfer

64-bit data transfer

How-to guides

•Configure AHB Trace Macrocell (HTM) Comparators