Debug HSM

In this topic:

Introduction

The HSM (Hardware Security Module) is an optional module available on selected AURIX devices.

The HSM protection is configured in the User Configuration Block (UCB). UCBs serve as vital repositories of critical settings and configurations that drive the behavior and functionality of SoC features. They play a pivotal role in ensuring unmatched configurability. UCBs allow developers to define and configure crucial settings such as:

•Reset vector

•RAM initialization

•Hardware Security Module (HSM) configuration

•Logic Built-In Self-Test (LBIST)

•FLASH protection

•etc.

Through winIDEA, you can program an HSM application and configure the UCB (User Configuration Block) which is required to enable the HSM on your AURIX device.

Preventing device lock

•Devices or cores can be locked or hidden by the silicon vendor. Refer to Device/core is hidden or locked for more information.

•Read your AURIX device reference manual carefully

•Be cautious when debugging the HSM core: programming or erasing HSM-reserved FLASH sectors may lock the device.

•Wrong UCB data can permanently lock the device. Use winIDEA Demo Mode before FLASH programming to check if all UCB sectors contain correct data.

•The number of UCB writes is limited. Check your TriCore device documentation for exact limits.

•Uncheck the <UCB_device> box once UCB is programmed.

•Use the Image Checker during UCB or HSM code programming.

•HSM application programming and UCB configuration must be done carefully. Misconfiguration can lock the chip.

Configuration steps

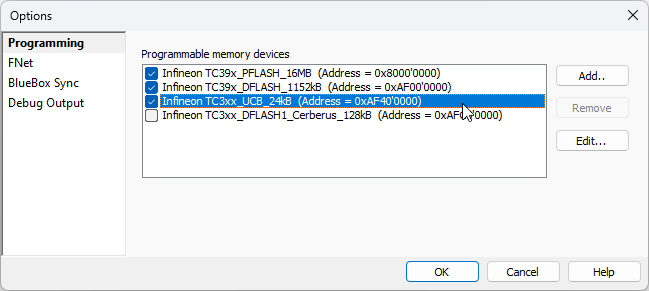

|

Enable UCB via Hardware Options | Programming. |

|

Make sure Automatically observe this core via Hardware | CPU Options | Cores HSM is checked. |

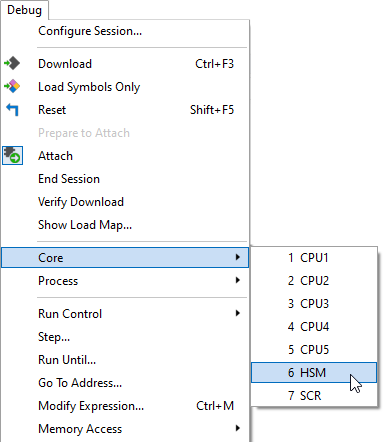

|

Open the secondary winIDEA instance via Debug | Core | HSM. |

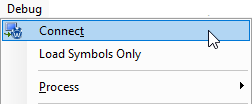

|

Connect to the primary winIDEA instance via Debug | Connect. |

When connected the Debug Status in winIDEA is:

•Primary: [CPU0] STOP

•Secondary: [HSM] STOP

More resources

•HSM - Troubleshooting tips

•Multi-Core Debugging - Overview

•Infineon TriCore AURIX TC3xx HSM - Debug & Timing Analysis - Webinar