Configure Arm Cortex-specific settings

In this topic:

•What information do you need before you start?

Introduction

This tutorial explains how to configure minimal architecture-specific settings required to start tracing.

What information do you need before you start?

Before you can start tracing, it is important to know the following:

•Does the CPU support trace?

•Are CPU trace pins available on target debug connector?

•Does the Debug Adapter/Active Probe and target debug connector match?

•Is the correct trace license programmed in the BlueBox?

Configuration steps

Your winIDEA workspace should be configured and the correct SoC Device selected in Debug | Configure Session | SoCs. Debug session needs to be established prior to using Trace. For more information, follow Getting started.

|

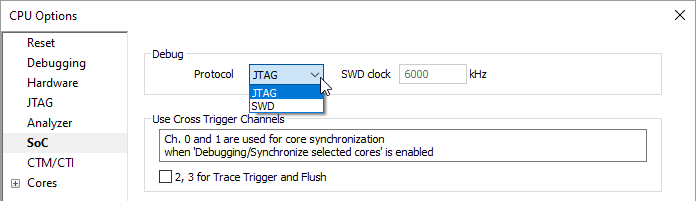

Select JTAG or SWD under the Debug Protocol via Hardware | CPU Options | SoC. |

|---|

Default SWD clock setting should work in most cases.

|

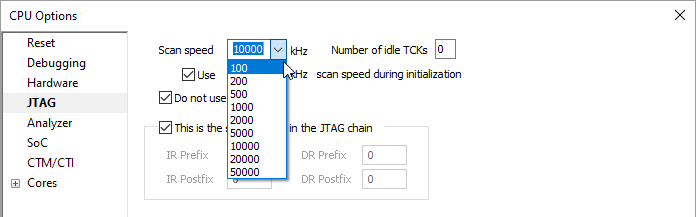

(optional) Set JTAG Scan speed via Hardware | CPU Options | JTAG. |

|---|

The page is visible only when the JTAG debug protocol is selected and confirmed. Default value 1000 kHz should work in most cases.

|

Open Hardware | CPU Options | Analyzer and set the Trace Operation mode. |

|---|

Optionally set the Cycle duration. This parameter is relevant for ETB On-Chip Trace Capture methods and timestamp calculation. Cycle duration is calculated based on the CPU clock.

|

Go to Hardware | CPU Options | SoC | Trace section and set the Trace Capture method. |

|---|

•SWO - This asynchronous trace is available only in combination with the SWD Debug Protocol as SWO signal is shared with the JTAG TDO pin.

•Parallel - Parallel (synchronous) trace is available in conjunction with both debug protocols, JTAG and SWD, and requires from 2 to 5 extra pins depending on the data trace size. Typical implementation is one clock line + 4 data lines. It features significantly higher trace output bandwidth comparing to the SWO trace, exact time information for recorded events and ETM (when available) support.

Next step