Initialize AMD Zynq UltraScale+ DDR RAM

In this topic:

Introduction

This topic describes how to download and run an application in DDR RAM on AMD Zynq UltraScale+ using winIDEA.

To execute and load an application to DDR RAM memory on AMD Zynq UltraScale+, DDR RAM memory needs to be properly initialized. In a regular or a production boot procedure, such initialization is usually done by one of the early-stage bootloaders. An example of such a bootloader for AMD Zynq UltraScale+ is the First Stage Bootloader (FSBL).

winIDEA can initialize DDR RAM memory by running a specified bootloader in SoC’ OCM RAM memory with an initialization script which is distributed with winIDEA in the SFR folder zynqUsp_enableDDR.cpp.

|

DDR RAM memory initialization and bootloader are use-case specific to the SoC and board, therefore bootloader applications (e.g., FSBL) are not distributed with winIDEA, and its parameters have to be configured manually. |

Requirements

•winIDEA 9.17.189 or newer

•BlueBox

•Active Probe or Debug Adapter

Configuration steps

Core which will run FSBL (and in turn do DDR initialization) is the same as set in Hardware | CPU Options | Reset | Configured boot core.

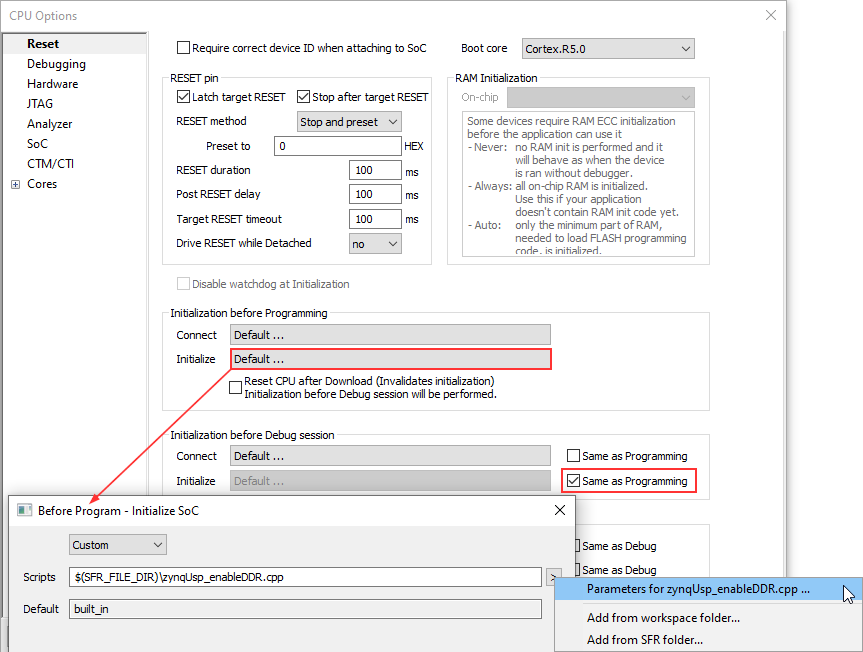

1. Add a custom script from the SFR folder in Hardware | CPU Options | Reset | Initialization before Programming | Initialize.

2. Select the script zynqUsp_enableDDR.cpp.

3. Select option Parameters zynqUsp_enableDDR.cpp via the arrow button.

4. Configure script parameters in the Edit options dialog:.

•g_FSBL_entry – Entry point of the FSBL bootloader application (default: 0xFFFC’0000).

•g_FSBL_offset – When programming FSBL to the memory this offset is added to the download location (default: 0).

•g_disableMPUAndCaches – If this parameter is set to anything but 0 (default: 1):

oMPU, data and instruction caches are disabled for the primary Cortex-R5 core.

oArm Cortex-R5 SCTLR.V bit is set for the primary core, which means interrupt vectors are mapped to 0xFFFF’0000.

•g_setVectorHigh – If this parameter is set to anything but 0 (default: 0), Arm Cortex-R5 SCTLR.V bit is set for the primary core, which means interrupt vectors are mapped to 0xFFFF’0000.

•g_FSBL_img – Path to the FSBL bootloader for specific AMD Zynq UltraScale+ and the board.

5. Check option Same as Programming in Initialization before Debug session | Initialize section.

6. Perform Download to the DDR RAM memory and execution from it should be possible.