9.21.283

In this topic:

Verified build release date: 28 October 2024

Full winIDEA version: 9.21.283.1.192841

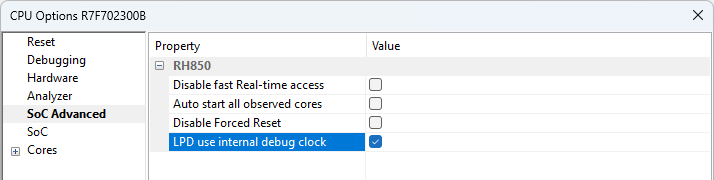

Renesas RH850: LPD use internal debug clock

You can now use LPD as internal debug clock for RH850 G4 devices without LPDCLKOUT return debug clock connected. To find this new feature go to Hardware | CPU Options | SoC Advanced.

See SoC Advanced for more details.

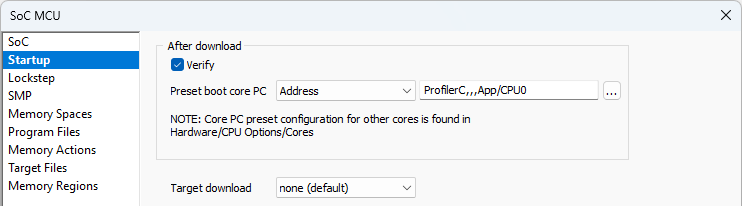

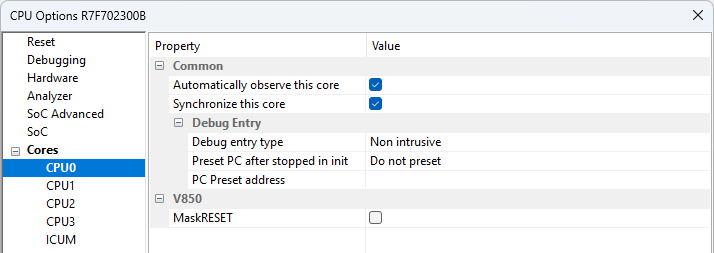

Debug Entry for boot core moved to Startup page

The configuration for the boot core PC preset, previously found in Hardware | CPU Options | Cores | <boot core>, was moved to Debug | Configure Session | SoCs | Startup. The option is also available in the Basic Session Configuration dialog. The PC preset for other cores remains in the CPU Options dialog.

Currently:

Previously:

TDK

HVC5x

Adding support.

Supported features:

•Debug: SWD, Cortex-M3, Internal WDOG disable EVE script

•SFR

•UMI: Internal

Variants:

•HVC5221D

•HVC5222C

•HVC5223C

•HVC5222D

•HVC5422D

winIDEA version: 9.21.275.0.189001

ChinaCore

CCFC3007

Adding support.

Supported features:

•Debug: JTAG, C3007, C2004, C2002 (HSM), multicore (core sync)

•SFR

•UMI: CFLASH, DFLASH

Variants:

•CCFC3007PTT192

•CCFC3007BCT192

•CCFC3007BCT64

winIDEA version: 9.21.276.0.189172

Renesas

RH850/U2A

Extending support.

Supported features:

•Debug: Challenge response

winIDEA version: 9.21.277.0.189501

RH850/U2B

Extending support.

Supported features:

•Debug: Challenge response

winIDEA version: 9.21.277.0.189501

Infineon

Traveo-II

Extending support.

Supported features:

•Debug port authentication

winIDEA version: 9.21.281.0.190826

Tongxin Micro

THA62x

Adding support.

Supported features:

•Debug: JTAG, SWD, 2x Cortex-R52+ (lockstep), multicore (core sync)

•SFR

•UMI: Cortex-R52 PFLASH, Cortex-R52 DFLASH

•Trace: Cortex-R52 ETM ETB

Variants:

•THA6206

winIDEA version: 9.21.282.0.191023

Refer to this document for more information.