Recorder

In this topic:

•Enable trace until CPU reset - Trace over HW reset

•Continuous mode - Trace over SW reset

Enable trace until CPU reset - Trace over HW reset

The trace buffer is cyclic and trace registers are reset together with the CPU, so it is impossible to determine where the trace recording has stopped (which message was first and which is last in EMEM RAM).

When this option is enabled, winIDEA uses time stamp information (counters stored in the trace buffer) to find the first and the last message.

If the relative timer (tsu_rel_en, tsu_rel_sync) is not set in the Trigger Configuration dialog / MCX page, the reset point cannot be determined.

|

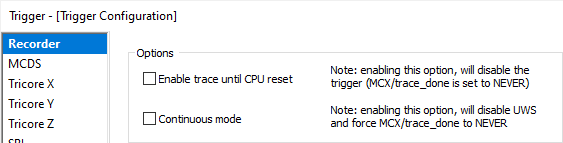

Enabling this option will disable the Trigger (MCX/trace_done is set to NEVER). |

|

Option Enable trace until CPU reset is working only when trace to EMEM is used. |

Continuous mode - Trace over SW reset

During SW reset, trace is working normally. Everything what is specified as qualifier is stored to trace RAM. To trace operation before and after reset you can either:

a)Set breakpoint to code which is executed after reset only and select Continuous mode in Trigger configuration dialog / Recorder page in winIDEA. In this mode Trigger (trace_done) is automatically set to NEVER and trigger position to END. After SW reset CPU stops at breakpoint, trace is stopped and history is visible.

b)Set the trace Trigger (trace_done) to function which is executed after reset only and trigger position to END. After SW reset trace trigger occurs, trace is stopped and history is visible. Note that SW reset can take a while so timestamp messages can fill on-chip trace memory RAM completely. Disable time stamps or decrease the frequency of time stamps (if tsu_rel is used increase the value of the TSUPRSCL).

Upload While Sampling (UWS)

Refer to Upload While Sampling.